I2C

简介

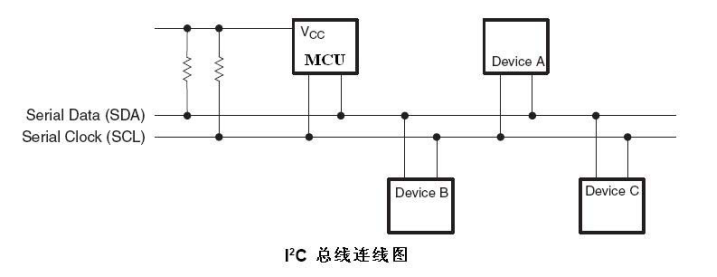

I2C(内部集成电路)是一种串行通信协议,允许将多个设备连接到一条总线上

I2C物理层

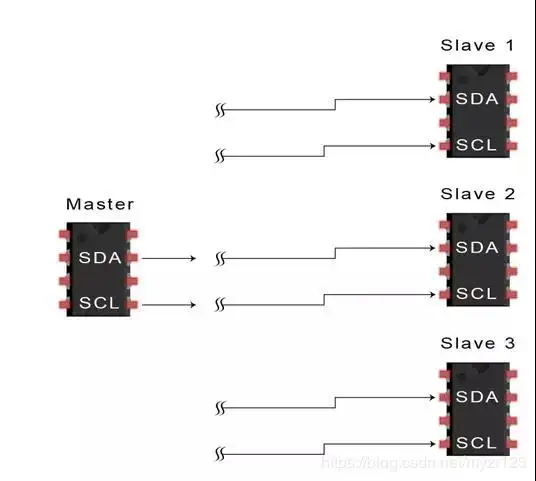

·它是一个支持设备的总线。“总线”指多个设备共用的信号线。在一个I2C通讯总线中,可连接多个I2C通讯设备,支持多个通讯主机及多个通讯从机。

·一个I2C总线只使用两条总线线路,一条双向串行数据线(SDA),一条串行时钟线(SCL)。数据线即用来表示数据,时钟线用于数据收发同步。

·每个连接到总线的设备都有一个独立的地址,主机可以利用这个地址进行不同设备之间的访问。

·总线通过上拉电阻接到电源。当I2C设备空闲时,会输出高阻态,而当所有设备都空闲,都输出高阻态时,由上拉电阻把总线拉成高电平。

·多个主机同时使用总线时,为了防止数据冲突,会利用仲裁方式决定由哪个设备占用总线。

·具有三种传输模式:标准模式传输速率为100kbit/s,快速模式为400kbit/s,高速模下可达3.4Mbit/s,但目前大多I2C设备尚不支持高速模式。

I2C协议层

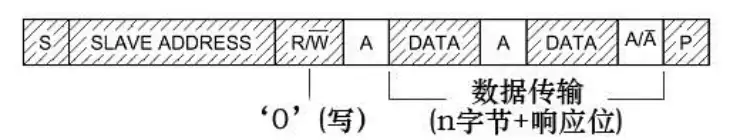

以主机向从机写数据为例,其基本结构如图所示,依次为:

起始信号——从机地址——读写信号——数据位——应答位——… … ——停止位

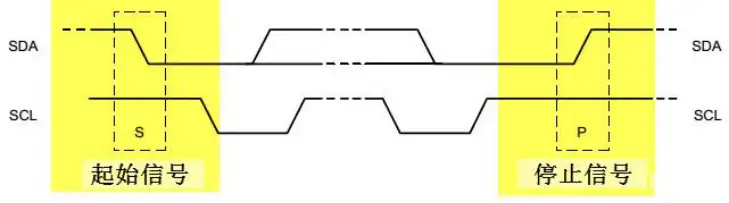

起始信号(S):当 SCL 线是高电平时,SDA 线从高电平向低电平切换;停止信号(P):当 SCL 是高电平时,SDA 线由低电平向高电平切换。

帧地址:I2C总线上的每个设备都有自己的独立地址,主机发起通讯时,通过SDA信号线发送设备地址(SLAVE_ADDRESS)来查找从机。I2C协议规定设备地址可以是7位或10位,实际中7位的地址应用比较广泛。

I2C使用SDA信号线来传输数据,使用SCL信号线进行数据同步。SDA数据线在SCL的每个时钟周期传输一位数据。传输时,SCL为高电平的时候SDA表示的数据有效,即此时的SDA为高电平时表示数据“1”,为低电平时表示数据“0”。当SCL为低电平时,SDA的数据无效,一般在这个时候SDA进行电平切换,为下一次表示数据做好准备。

I2C的数据和地址传输都带响应。响应包括“应答(ACK)”和“非应答(NACK)”两种信号。

作为数据接收端时,当设备(无论主从机)接收到I2C传输的一个字节数据或地址后,若希望对方继续发送数据,则需要向对方发送“应答(ACK)”信号,发送方会继续发送下一个数据;若接收端希望结束数据传输,则向对方发送“非应答(NACK)”信号,发送方接收到该信号后会产生一个停止信号,结束信号传输。

I2C功能框图剖析

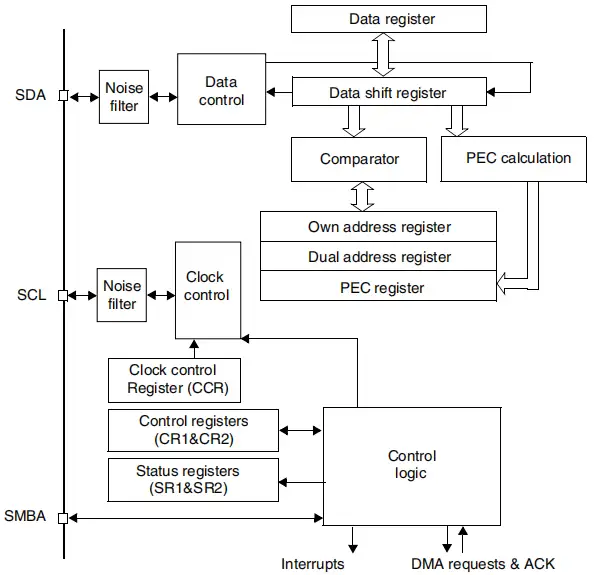

时钟控制逻辑:

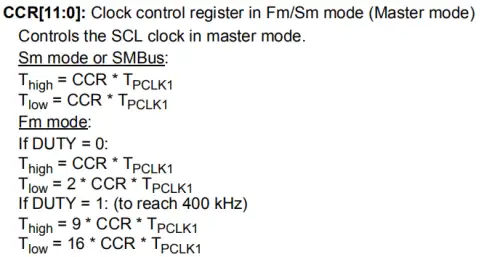

SCL线的时钟信号,由I2C接口根据时钟控制寄存器(CCR)控制,控制的参数主要为时钟频率。配置I2C的CCR寄存器可修改通讯速率相关的参数。

可选择I2C通讯的“标准/快速”模式,这两个模式分别I2C对应100/400Kbit/s的通讯速率。

在快速模式下可选择SCL时钟的占空比,可选Tlow/Thigh=2或Tlow/Thigh=16/9模式,我们知道I2C协议在SCL高电平时对SDA信号采样,SCL低电平时SDA准备下一个数据,修改SCL 的高低电平比会影响数据采样,但其实这两个模式的比例差别并不大,若不是要求非常严格,随便选就可以了。

CCR寄存器中还有一个12位的配置因子CCR,它与I2C外设的输入时钟源共同作用,产生SCL时钟,STM32的I2C外设都挂载在APB1总线上,使用APB1的时钟源PCLK1,SCL信号线的输出时钟公式如下:

例如,我们的PCLK1=36MHz,想要配置400Kbit/s的速率,计算方式如下:

PCLK时钟周期:TPCLK1 = 1/36000000

目标SCL时钟周期:TSCL = 1/400000

SCL时钟周期内的高电平时间:THIGH = TSCL/3

SCL时钟周期内的低电平时间:TLOW = 2*TSCL/3

计算CCR的值:CCR = THIGH/TPCLK1 = 30

计算结果得出CCR为30,向该寄存器位写入此值则可以控制IIC的通讯速率为400KHz,其实即使配置出来的SCL时钟不完全等于标准的400KHz,IIC通讯的正确性也不会受到影响,因为所有数据通讯都是由SCL协调的,只要它的时钟频率不远高于标准即可。

数据控制逻辑:

I2C的SDA信号主要连到数据移位寄存器上,数据移位寄存器的数据来源及目标是数据寄存器(DR)、地址寄存器(OAR)、PEC寄存器以及SDA数据线。当向外发送数据的时候,数据移位寄存器以“数据寄存器”为数据源,把数据一位一位地通过SDA信号线发送出去;当从外部接收数据的时候,数据移位寄存器把SDA信号线采样到的数据一位位地存储到“数据寄存器”中。若使能了数据校验,接收到的数据会经过PCE计算器运算,运算结果存储在“PEC 寄存器”中。当STM32的I2C工作在从机模式的时候,接收到设备地址信号时,数据移位寄存器会把接收到的地址与STM32的自身的“I2C地址寄存器”的值作比较,以便响应主机的寻址。STM32的自身I2C地址可通过修改“自身地址寄存器”修改,支持同时使用两个I2C设备地址,两个地址分别存储在OAR1和OAR2中。

整体控制逻辑:

整体控制逻辑负责协调整个I2C外设,控制逻辑的工作模式根据我们配置的“控制寄存器(CR1/CR2)”的参数而改变。在外设工作时,控制逻辑会根据外设的工作状态修改“状态寄存器(SR1和SR2)”,我们只要读取这些寄存器相关的寄存器位,就可以了解I2C的工作状态。除此之外,控制逻辑还根据要求,负责控制产生I2C中断信号、DMA请求及各种I2C的通讯信号(起始、停止、响应信号等)。

通讯过程

使用I2C外设通讯时,在通讯的不同阶段它会对“状态寄存器(SR1及SR2)”的不同数据位写入参数,我们通过读取这些寄存器标志来了解通讯状态。

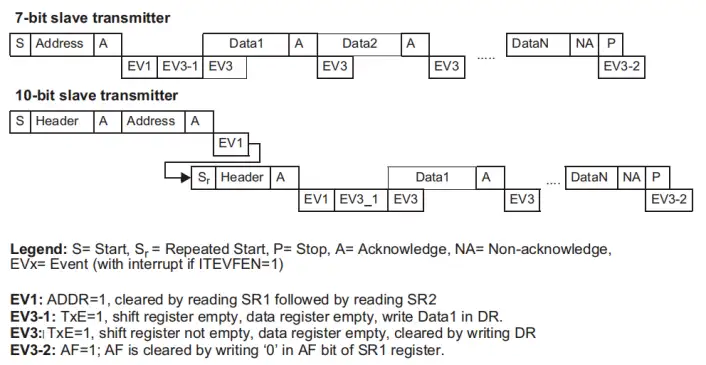

从发送模式:

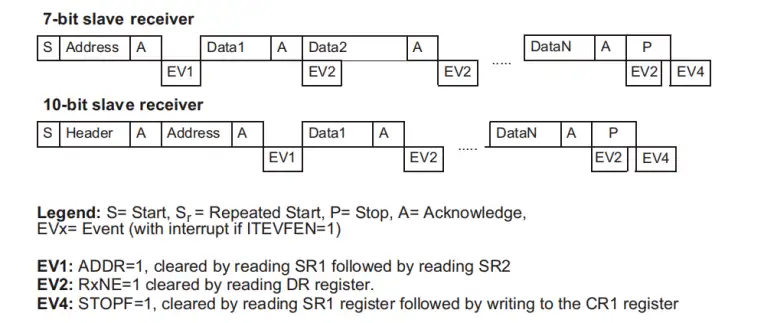

从接收模式:

I2C

Intro

IC (Inter-Integrated Circuit) is a

Synchronous

multi-master

multi-slave

packet switched

single-ended

serial computer bus invented in 1982 by Philips Semiconductor

It is widely used for attaching lower-speed peripheral Is to processors and microcontrollers in short-distance, intra-board communication.

Inter-Integrated Circuit, or I2C

- I2C combines the best features of SPI and UART.

- With I2C, we can connect multiple slaves to a single master (like SPI) and we can have multiple masters controlling single, or multiple slaves.

- I2C is really useful when you want to have more than one microcontroller logging data to a single memory card or displaying text to a single LCD

- Like UART communication, I2C only uses two wires to transmit data between devices

Architecture

- Half-duplex, synchronous, multi-master bus

- No chip select or arbitration logic required

- Serial data (SDA) and Serial clock (SCL)

Features

- Each peripheral is known as a “node” and can act as either a master or a slave

- The master controls the data transfer and generates the clock signal

- The slave is any device addressed by the master

- More than one microcontroller can be connected to the bus, and they can claim the master role at different times.

- The protocol uses the serial data line (SDA) and serial clock line (SCL) signals to support serial communication of 8-bit data bytes, 7- bit device addresses as well as control information

- All data is transferred in blocks of 8 bits (a byte), with no limit on the number of bytes that can be transferred in a message

- Each byte is followed by a 1 bit acknowledgement from the receiver.

Definition

Master – the device that initiates communication and controls the clock.

- Multiple masters are also supported on an I2C bus.

Slave – a device on the bus that is read or written to, but does not initiate transmission or provide a clock.

Slave address – a unique and predetermined address for each slave on the bus.

- This address is used by the master to indicate which slave it wants to communicate with.

SDA (Serial Data) – The line for the master and slave to send and receive data.

SCL (Serial Clock) – The line that carries the clock signal.

I2C is a serial communication protocol, so data is transferred bit by bit along a single wire (the SDA line).

Like SPI, I2C is synchronous(同步的), so the output of bits is synchronized to the sampling of bits by a clock signal shared between the master and the slave.

The clock signal is always controlled by the master.

Principle

The I2C standard is a serial interface implement with a two- wire link that can support multiple masters and multiple slaves

I2C uses two bi directional open collector BJT or open drain of MOSFET lines

It behave like a switch and can have possibly two states- ON or OFF

定义

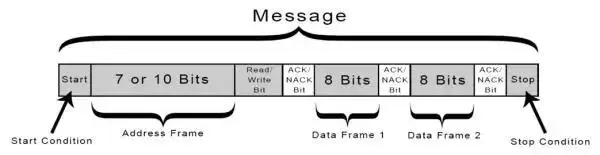

使用I2C时,数据被转换成messages,messages则被分解为数据帧。每条messages都有一个地址帧,其中包含从站的二进制地址,以及一个或多个包含正在传输的数据的数据帧。该消息还包括每个数据帧之间的启动和停止条件,读/写位和ACK / NACK位:

启动条件:在SCL线路从高电平切换到低电平之前,SDA线路从高电平切换到低电平。

停止条件:SCL线路从低电平切换到高电平后,SDA线路从低电平切换到高电平。

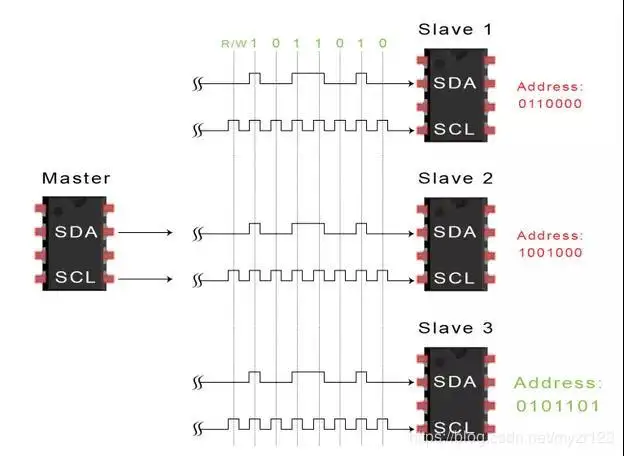

地址帧:每个从站唯一的7或10位序列,用于在主站想与之通信时识别从站。

读/写位:单个位,指定主器件是向从器件发送数据(低电压电平)还是从器件请求数据(高电压电平)。

ACK / NACK位:消息中的每个帧后跟一个应答/不应答位。如果成功接收到地址帧或数据帧,则从接收设备向发送方返回ACK位。

地址

I2C没有像SPI这样的从选择线,因此它需要另一种方法让从器件知道数据正在发送给它,而不是另一个从器件。它通过地址来做到这一点。地址帧始终是新消息中起始位之后的第一帧。

主设备将与其通信的从设备的地址发送给与其连接的每个从设备。然后,每个从设备将从主设备发送的地址与其自己的地址进行比较。如果地址匹配,则将低电压ACK位发送回主机。如果地址不匹配,则从器件不执行任何操作,SDA线保持高电平。

The LSB of the address byte is the direction control bit ◦

- High = read

- Low = write

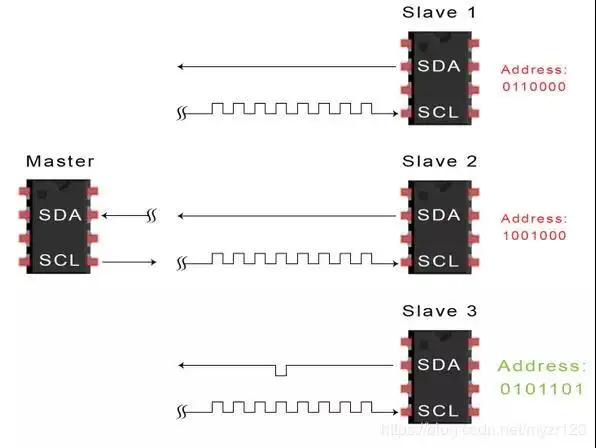

读/写位

地址帧在末尾包括一个位,用于通知从设备,主设备是想要向其写入数据还是从主设备接收数据。如果主设备想要向从设备发送数据,则读/写位是低电平。如果主设备向从设备请求数据,则该位是高电平。

- When the master is writing to a slave, the master sends the 8-bits of data and the slave produces the ACK/NACK signal.

- When the master is reading from a slave, the slave sends the 8-bits of data and the master produces the ACK/NACK

signal.

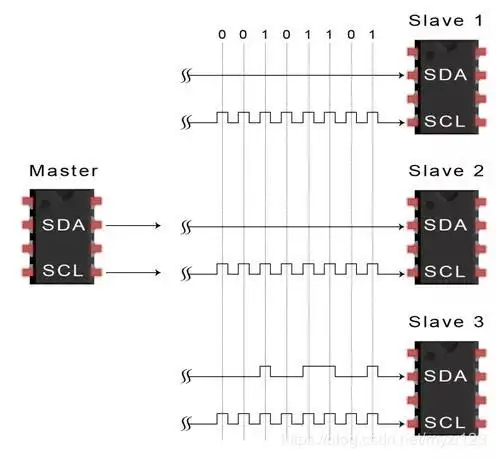

数据框架

在主设备检测到来自从设备的ACK位之后,准备好发送第一个数据帧。

数据帧始终为8位长,并以最高有效位先发送。紧接着每个数据帧的ACK / NACK位以验证帧已被成功接收。在发送下一个数据帧之前,主机或从机必须接收ACK位(取决于发送数据的人)。

在发送了所有数据帧之后,主设备可以向从设备发送停止条件以停止传输。停止条件是SCL线上从低电平到高电平转换后,SDA线上从低电平变为高电平,SCL线保持高电平。

特点

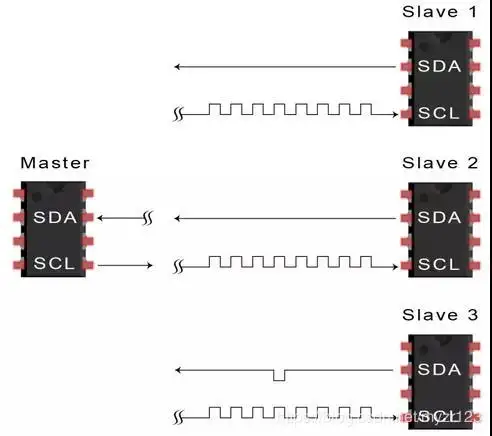

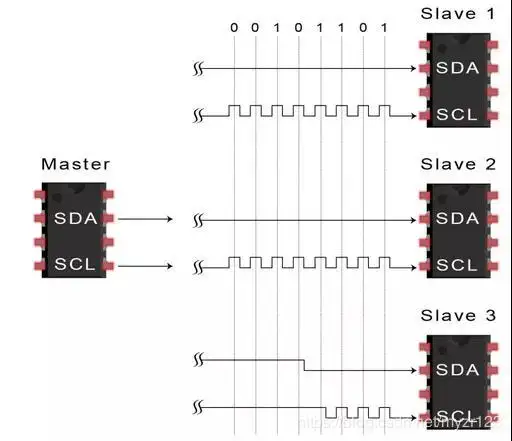

一主多从

由于I2C使用寻址,因此可以从单个主设备控制多个从设备。使用7位地址,可以使用128(27)个唯一地址。使用10位地址并不常见,但提供1,024(210)个唯一地址。要将多个从器件连接到单个主器件,请像这样连接它们,使用4.7K欧姆上拉电阻将SDA和SCL线连接到Vcc

多主多从

多个主设备可以连接到单个从设备或多个从设备。当两个主设备尝试通过SDA线同时发送或接收数据时,同一系统中出现多个主设备的问题。为了解决这个问题,每个主设备需要在发送消息之前检测SDA线路是低还是高。如果SDA线为低电平,则表示另一个主控制器已控制总线,主控制器应等待发送消息。如果SDA线路很高,那么传输信息是安全的。要将多个主设备连接到多个从设备,请使用下图,使用4.7K欧姆上拉电阻将SDA和SCL线路连接到Vcc

Clock Stretching

12C devices can slow down communication by stretching SCL

- kind of flow control

- If an addressed slave device is not ready to process more data it will stretch the clock

The master will not be able to raise the clock line

Steps

- 主机向每一个连接的从设备发送数据,然后将SDA信号从高切换到低,之后在将SCL从高切换到低电平。

- 主设备向每个从设备发送它想要与之通信的从设备的7或10位地址,以及读/写位:

- 每个从设备将主设备发送的地址与其自己的地址进行比较。如果地址匹配,则从器件通过将SDA线拉低一位来返回ACK位。如果主设备的地址与从设备的地址不匹配,则从设备将SDA线保持为高电平。

- 主设备发送或接收数据帧:

- 在传输了每个数据帧之后,接收设备将另一个ACK位返回给发送方以确认成功接收到该帧:

- 要停止数据传输,主机通过在将SDA切换为高电平之前切换SCL为高电平来向从机发送停止条件:

To stop the data transmission, the master sends a stop condition to the slave by switching SCL high before switching SDA high

Idle – when both SDA and SCL are held high by the pull-up resistors and no I2C device is attempting to communicate.

Busy – when devices are driving the bus.

Messages – how I2C information is transferred.

Pros and Cons

优点

只使用两根电线

支持多个主服务器和多个从服务器

ACK / NACK位确认每个帧都已成功传输

硬件没有UART那么复杂

众所周知且广泛使用的协议

缺点

数据传输速率比SPI慢

数据帧的大小限制为8位

实现比SPI更复杂的硬件